Video

RISC

Reduced Instruction Set Computer

The RISC architecture was designed to prioritise processor efficiency and the expense programmer ease of use. This meant that they tended toward usage where efficiency is paramount.

Key Features

- Commonly used in Smartphones (ARM/Snapdragon Processors), some supercomputers

- Machine oriented

- 1 Instruction per cycle

- Fixed Instruction Size in memory so we can use pipelining

- RISC does not do any operations directly in memory

- Highly efficient & optimised – Low power consumption

- Many more lines of code

- Each task is broken into simple instructions

- Extensive use of general purpose registers

- Simplified instruction set

- Few addressing modes available

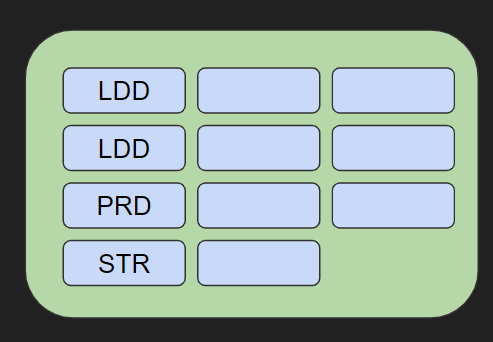

Example RISC Multiply Instruction

Multiplying two numbers in memory requires 2 lines of code.

CISC

Complex Instruction Set Computer

The CISC architecture sacrifices some processor efficiency for the sake of ease of development and flexibility.

- Commonly Used in desktops and servers (Intel Processors)

- Programmer oriented

- Variable Instruction sizes in memory

- Processes more complex instructions

- 1 Instructions may take more than one cycle

- Many addressing modes available

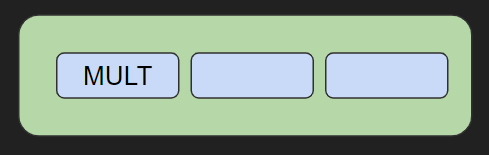

Example CISC Multiply Instruction

Multiplying 2 numbers in memory requires only 1 line of code.

Interrupt Handling

Challenge

Programming Challenge

Today’s challenge is to create a quiz in Python. For each question the program should display a statement about RISC/CISC architecture. The user needs to read the statement and decide which one it applies to.

- The quiz should have a time limit.

- The quiz statements should be loaded from a CSV file.

- The quiz should display how many questions they got right within the time limit, accuracy, answers per second, display a list of statements that were wrong.

- The quiz should store player names and scores.

- The quiz should display high scores.

Resources