Introduction

Introduction

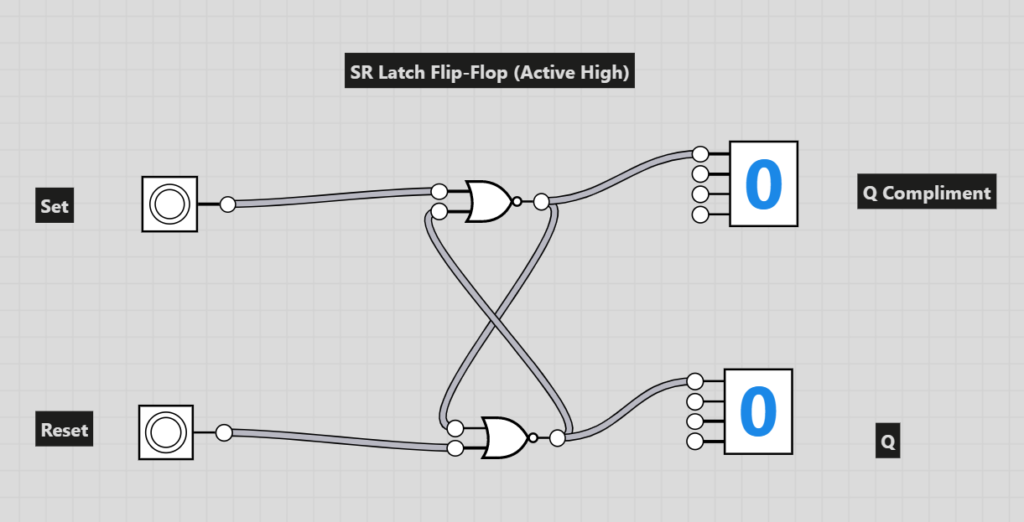

SR Flip Flop (Active High)

SR Flip Flop (Active High)

- Consists of two NOR gates

- The inputs are both normally set to Low.

- Only pulses of high set or reset the flip flop.

- Sending a pulse on Set sets Q to high and Q Compliment to Low

- Sending a pulse on Reset sets Q to low and Q Compliment to high.

Tutorial Video

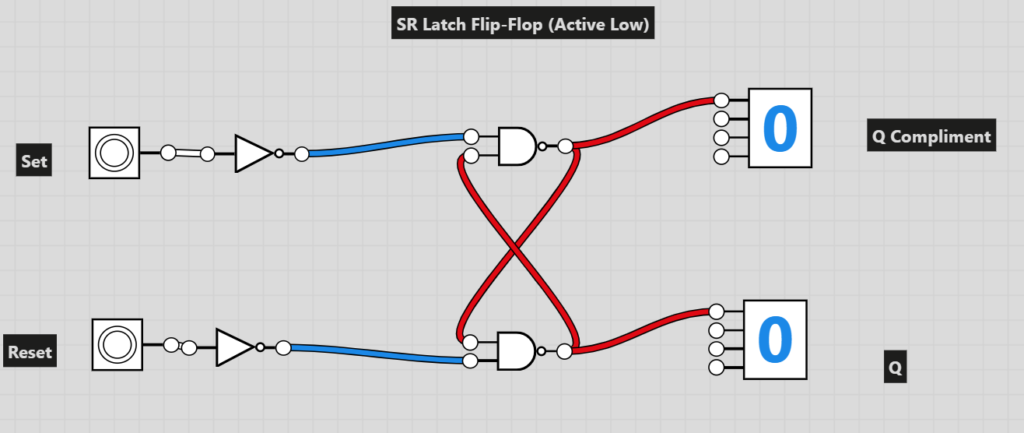

SR Flip-Flop (Active Low)

SR Flip-Flop (Active Low)

- Consists of two NAND gates

- The inputs are both normally set to High.

- Only pulses of low set or reset.

- Sending a pulse on Set sets Q to high and Q Compliment to Low

- Sending a pulse on Reset sets Q to low and Q Compliment to high.

JK Flip-Flop

The problem with SR Flip Flops

A problem with the SR flip flop occurs when both the Set and Reset inputs receive pulses at the same time. This would result in a race condition where both the Q and Q Complement are trying to toggle each other. The end result would be an invalid state (Either 0-0 or 1-1).

In order rectify the problem the JK flip-flop can be used instead.

JK Flip Flop

Past Paper Questions