Introduction

Introduction to Processor Pipelining

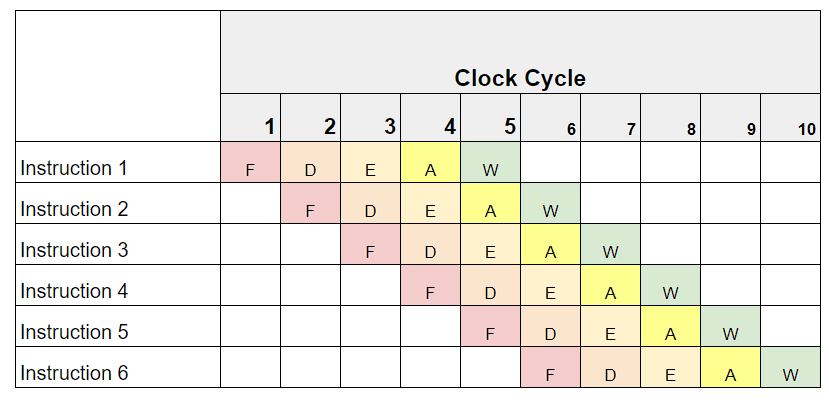

Processor pipelining breaks down the execution of instructions into a series of sequential stages.

Each stage performs a specific task, and multiple instructions are processed simultaneously, with each instruction progressing through the pipeline stages one after the other.

Stages

Pipelining Stages

Typical pipeline stages include:

- instruction fetch

- instruction decode

- execution

- memory access

- write back

These stages represent different tasks involved in the execution of instructions.

The number of stages in the pipeline is known as the pipeline depth. Deeper pipelines allow for finer-grained parallelism but may increase the impact of hazards and introduce latency due to pipeline stages.

Parallelism & Overlap

Pipelining Parallelism & Overlap

Pipelining exploits instruction-level parallelism by allowing different stages of different instructions to be executed concurrently.

As one instruction completes its execution in one stage, the next instruction enters the pipeline, maximizing CPU utilization through instruction overlap.

Advantages

Advantages of Pipelining

Increased Throughput

Pipelining allows multiple instructions to be executed concurrently, leading to higher throughput and improved performance.

Efficient Resource Utilization

By overlapping the execution of different instructions, pipelining maximizes the utilization of CPU resources, leading to better overall efficiency.

Faster Execution

Pipelining reduces the overall time taken to execute a sequence of instructions by allowing multiple instructions to progress simultaneously through different pipeline stages.

Scalability

Pipelining can be scaled to accommodate different levels of complexity and performance requirements, making it suitable for a wide range of computing environments.

Disadvantages

Disadvantages of Pipelining

Pipeline Hazards

Introduce data, control, and structural hazards, leading to pipeline stalls and reduced efficiency.

Complexity

Design and implementation complexity due to managing pipeline stages, hazard detection, and inter-stage communication.

Latency

Deeper pipelines may increase latency due to signal propagation through multiple stages, affecting responsiveness.

Branch Prediction Challenges

Branches can disrupt instruction flow, leading to pipeline flushing or mispredictions, impacting performance.