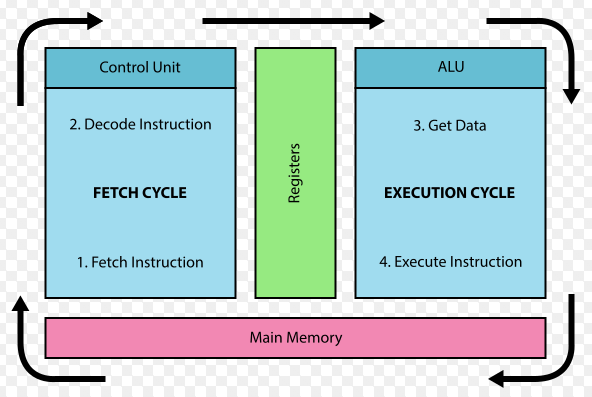

Fetch Decode Execute Cycle

The fetch decode execute cycle is the process the computer goes through when processing instructions. The cycle is performed constantly from boot up, until the computer is shutdown.

Fetch Phase

In this phase of the cycle, the processor:

- Gets the memory address of the current instruction from the program counter PC

- Passes the address to the memory address register

- Sends the address along the address bus.

- The RAM retrieves the data stored at that address and passes the data back along the data bus.

- The data is the stored in the memory data register (MDR) ready for decoding.

Decode Phase

In this phase the data in the MDR is passed to the control unit (CU) which then decodes the instruction and then signals to the ALU what instruction is to be completed.

Execute Phase

In the final phase of the fetch decode execute cycle the instruction is executed.

This instruction could comprise of:

- Reading operand data in to the accumulator from the RAM

- Performing arithmetic on operand data

- Performing logical functions (conditionals / loops)

- Writing data from the accumulator to the RAM

Once this step is complete the CPU moves on to the next instruction

Operands vs Opcodes

An opcode is a single instruction that tells the process what operation to perform. An operand is the data or location on which the operation will be performed.

ADD 4

Opcode = ADD Operand = 4 – This means add the number stored at memory location 4 to the number stored in the accumulator.

Full Example

- LOAD 3

- SUB 4

- STORE 5

This example means:

- load the contents of memory location 3 in to the accumulator

- Subtract the contents of memory location 4 from the data in the accumulator

- Store the result of the subtraction to memory location 5